Double side redistribution layer process on embedded wafer level package for package on package (PoP) applications | Semantic Scholar

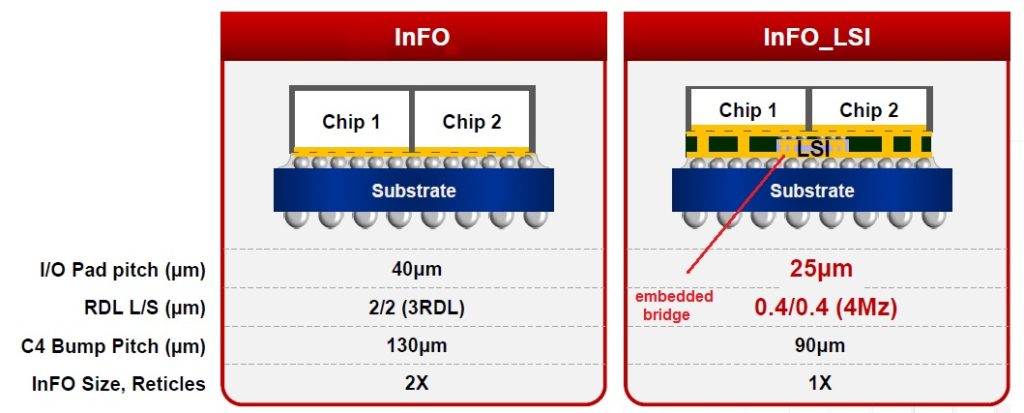

InFO (Integrated Fan-Out) Wafer Level Packaging - Taiwan Semiconductor Manufacturing Company Limited

Double side redistribution layer process on embedded wafer level package for package on package (PoP) applications | Semantic Scholar

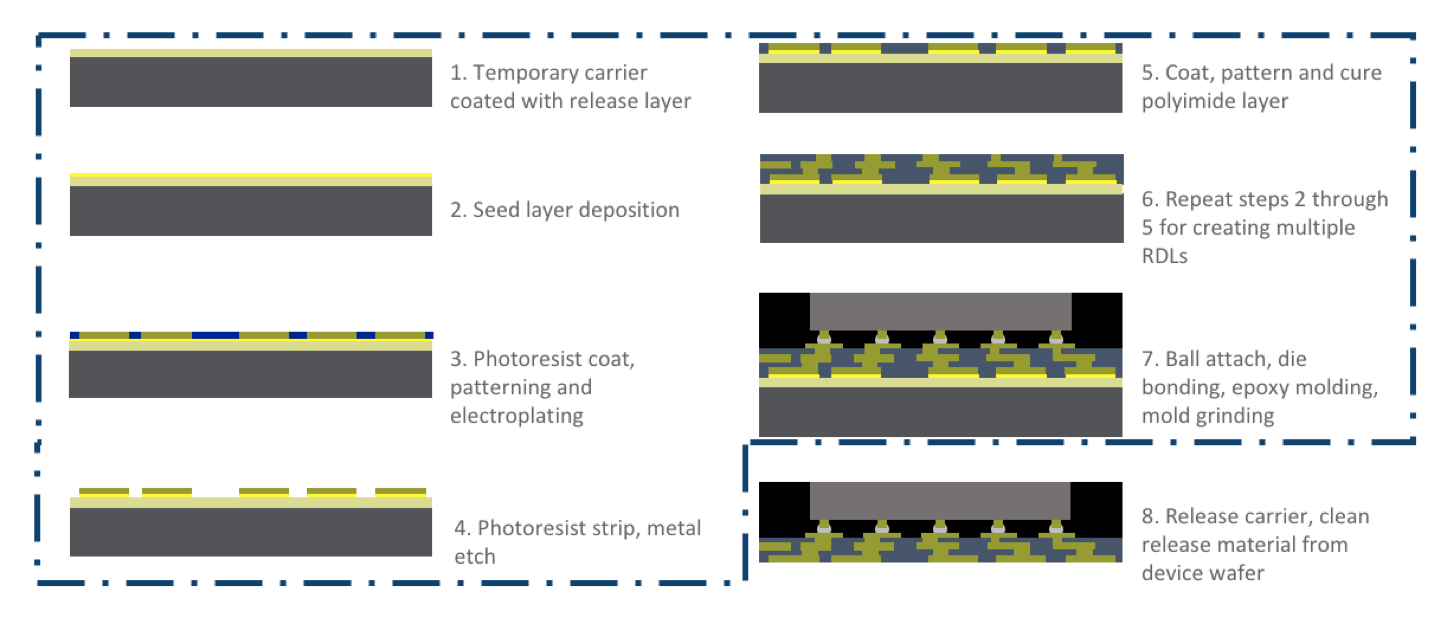

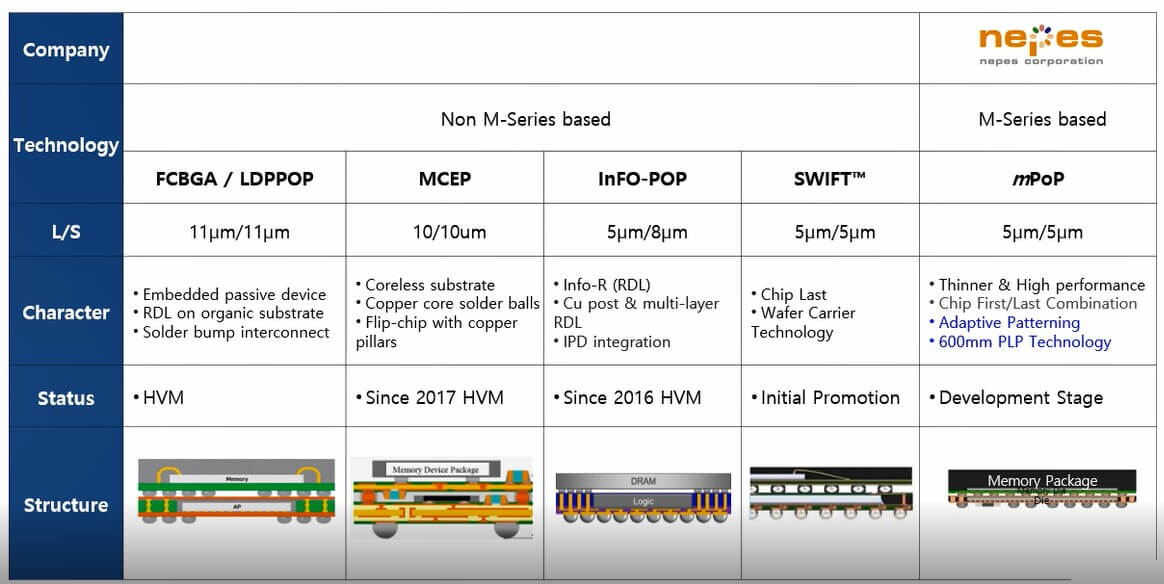

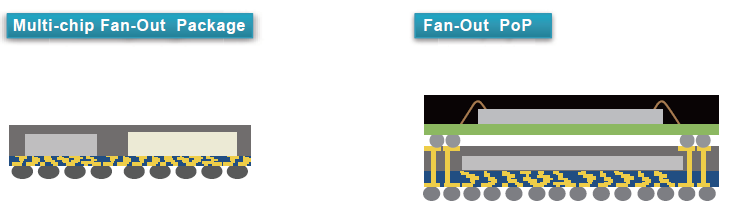

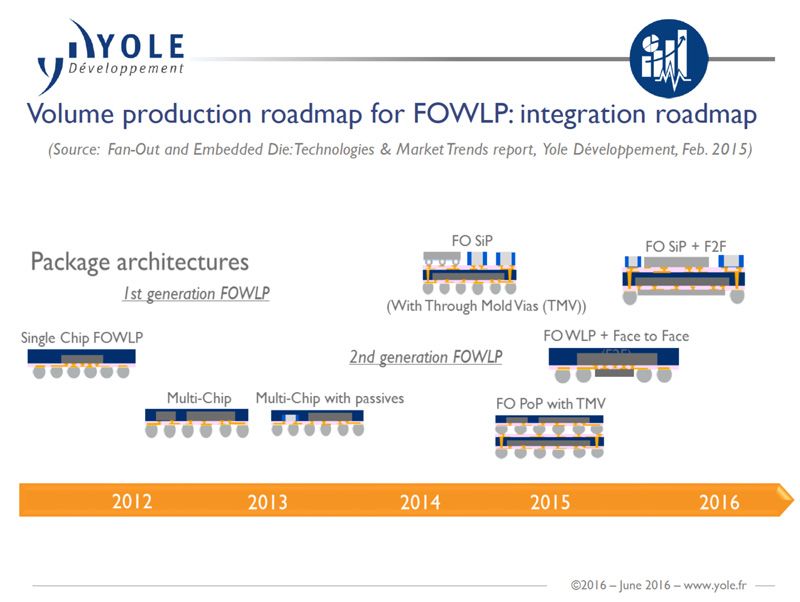

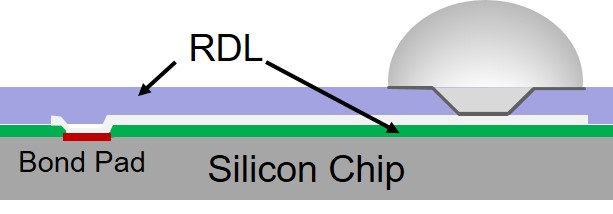

Polymers in Electronics Part Six: Redistribution Layers for Fan-Out Wafer Level Packaging - Polymer Innovation Blog

Double side redistribution layer process on embedded wafer level package for package on package (PoP) applications | Semantic Scholar

Double side redistribution layer process on embedded wafer level package for package on package (PoP) applications | Semantic Scholar